光刻中Overlay技术详解

随着半导体工艺节点迈向5nm、3nm及更先进水平,晶圆上各层图案的对准精度(Overlay)成为影响良率和性能的关键因素。任何微小的对准误差都可能导致电路失效或性能下降。

面对日益复杂的器件结构,Overlay测量工具在不断提升精度的同时,也成功维持了可接受的测量效率,满足了先进制程的双重需求。先进制程的Overlay容差正迅速收紧。例如,在3nm节点(金属间距约22nm),对准精度已进入个位数纳米级别。为确保5nm和3nm节点的良率,业界正采用新的测量目标设计、机器学习方法及更先进的光学测量系统,以加速关键检测流程。

1. Overlay介绍

Overlay指两个或多个光刻层图案能否精确叠加。每层图案必须与下层结构准确对准,否则将导致连接错位或断点,使器件失效。以3nm节点为例,金属线宽仅约20nm,Overlay容差需控制在2nm以内。如此高的精度要求,对光刻设备、测量工具和工艺控制构成巨大挑战。

Overlay精度已成为影响芯片良率的关键因素之一。其核心目标是确保每层掩膜图形与下方图形的精准对准。在5nm等先进节点,Overlay容差通常仅为图形尺寸的30%,必须严格控制在几纳米内以保证良率。

一个典型芯片包含超过50层掩膜。部分关键层采用极紫外(EUV, 13.5nm)曝光,非关键层则使用深紫外(193nm)曝光。EUV曝光设备、检测系统及算法的关键技术进展,共同提升了Overlay控制能力,实现了更高良率。

Overlay技术发展趋势包括:

1. 采用近红外(near IR)对准: 穿透新型硬掩膜材料(尤其是可见光不透明材料),提高测量精度。

2. 设计更贴近电路结构的测量目标: 提升实际应用中的测量准确性。

3. 提高测量采样密度: 增加数据点覆盖,提升测量代表性和准确性。

4. 应用机器学习算法: 加速数据处理,优化在线检测,减少人工干预和误差。

此外,硬件改进(如晶圆吸附盘升级)也在持续优化精度,抵消晶圆弯曲等影响。这些技术进步共同推动Overlay测量精度提升,为先进芯片制造提供坚实支持。

2. EUV光刻的技术挑战与进展

EUV光刻使用13.5nm波长实现更小图形尺寸,但也带来新的Overlay挑战:

● 光学系统复杂: 反射式设计增加光路复杂性,易引入图形畸变。

● 掩模热变形: 曝光过程中掩模易发热变形,影响图形准确性。

● 随机性效应增强: 光子数量减少导致图形边缘粗糙度增加。

EUV工具层面的技术进展对实现高精度Overlay至关重要。光刻不仅需高分辨率打印微小图形,还必须确保层间精准对准。

为实现此目标,晶圆和掩膜上会刻有微小对准标记,供光刻机内部工作台精确定位。设备以扫描方式完成掩膜图案曝光,每次曝光后移动至下一芯片位置重新对准,直至整片晶圆完成。

Overlay测量主要通过两种光学系统完成:显影后检测(ADI) 和 蚀刻后检测(AEI)。存储芯片加速采用AEI,因其在3D结构(如通道孔)中能更显著反映蚀刻过程引入的偏差。逻辑芯片因器件特征多样,选择代表性特征困难,更多依赖ADI。

每台EUV光刻设备通常配备2至4台Overlay测量设备。常见的测量方法包括基于图像的Overlay(IBO)和基于衍射的Overlay(DBO/散射计量),部分系统结合使用两者。

测量目标通常设计为上下两个光栅结构。通过调整角度成像并检测边缘差异产生信号,实现高精度测量。系统结合ADI和AEI反馈数据,以及光刻机内部传感器信息,进行补偿校正(如平移、旋转及更高阶误差)。光刻机在扫描过程中能进行高阶误差补偿。测量目标通常置于芯片间的切割道(scribe line)区域。测量点越多,运动补偿越精细,精度控制能力越强。

3. 边缘定位误差(EPE)

随着器件特征缩小和掩膜层数增加,Overlay容差预算不断缩减。随机性效应加剧了这一问题,进一步降低了Overlay和关键尺寸(CD)的测量精度。

边缘定位误差(EPE)指晶圆上理想图案与实际制造图案的偏差,主要来源(按重要性排序):

1. CD均匀性中的随机性误差(如线宽/线边粗糙度)。

2. 光学邻近效应校正(OPC)引起的CD偏差。

3. 全局CD不均匀性。

4. Overlay误差本身。

目前EPE最大来源是难以控制的随机性误差,因此相对可控的Overlay误差成为关注重点。这意味着晶圆厂需要制造EPE极小的器件,但可用于控制Overlay和CD均匀性的预算已不足。因此,对Overlay和CD精度的要求更严苛且提升更快。

业界应对措施包括:

● 提高光学Overlay采样频率。

● 改进现有Overlay测量技术。

● 引入基于扫描电镜(SEM)的Overlay测量技术(适用于ADI和AEI)。

传统光学计量工具通常使用500-650nm波长光源。新技术使用900nm长波长激光,能穿透光学不透明的硬掩膜层(如部分存储芯片层),扩大了测量工具的适用范围。计量系统的灵活性和技术升级对满足不断变化的制程需求至关重要。

4. Overlay测量与校准

测量与校准是确保光刻精度的关键步骤。首次图形定位检查通常在光刻胶显影后(ADI)。若此时发现Overlay超差,晶圆可返工修复。量产中,晶圆厂通常每批次监控约6片晶圆的CD均匀性和Overlay。

现代Overlay监控依赖大量数据采集与分析处理,实现实时监测与校准。通常从晶圆切割道中的测量目标采集数据。必须理解测量数据与器件区域实际Overlay(即器件Overlay)的关系。

由于测量目标图案间距(几百纳米)远大于器件图案间距(约20-30纳米),存在测量目标到器件的偏差(MTD offset),需要进行测量和校准以确保精准定位。

此外,EUV工艺中可能存在局部随机误差(量级达几纳米),通常使用电子束(e-beam)系统测量。结合CD误差和Overlay误差,整体图形定位误差可达4-5纳米。电子显微镜(SEM)用于捕获这些局部随机误差,结合Overlay测量结果,对曝光系统进行校正。电子束成像可提供埃(Å)级分辨率的高精度测量。

测量精度高度依赖目标设计。目标通常置于切割道或器件内特定区域,由多层薄膜堆叠和宽线距光栅图案构成,以适配当前工艺层次并反映器件偏差。为满足更高精度要求,目标正向更小、更精细迁移(如尺寸缩小至4-8微米,远小于传统的25微米目标)。新设计(如利用莫尔条纹效应的目标)具有更高灵敏度。

5. 先进过程控制(APC)

APC是确保制造高精度与稳定性的关键技术。光刻前,通过扫描仪实时测量晶圆形貌,可优化曝光质量并为控制环路提供关键反馈(如识别对焦不均引起的局部Overlay偏差)。

结合物理建模与机器学习的计算Overlay校正技术正在发展。它能在无直接测量的情况下,通过扫描仪数据预测晶圆或批次的Overlay偏差,提供更具前瞻性的优化手段。

行业正转向更高密度的晶圆抽样,以更全面捕捉晶圆内特征分布和批次间差异。这在ADI和AEI中都日益重要。电子束工具尤其关注影响精密工艺稳定性的局部图形定位误差。提高抽样密度对提升测量精度、识别晶圆内变化至关重要,电子束设备可同时在多层测量EPE和CD。

ADI与AEI之间的相关性是过程控制的基础。精确掌握两者关系能有效优化整体控制能力,确保持续提升制程精度。

ADI和AEI是Overlay控制的两个关键环节:ADI适合前端快速修正,AEI更贴近真实结构偏移,二者协同构建了先进工艺中精密的图案对准闭环系统。Overlay误差是EPE控制的核心变量,决定了最终芯片图案的精度与可靠性。

6. 结语

在先进制程中,Overlay控制的核心是实现快速数据反馈以进行及时误差补偿,确保曝光高精度。然而,下一代EUV技术——高数值孔径(High-NA)EUV的引入将带来新挑战。

High-NA EUV采用非等距放大技术(一个方向放大8倍,另一方向放大4倍),导致曝光区域减半,需要在晶圆上进行两片掩模图形的拼接(stitching),对精度和同步性要求更高。随着High-NA EUV发展,Overlay控制的技术难度将进一步提升,特别是在高精度图形拼接和误差补偿方面。业界正通过精确算法和先进光学设计推动技术进步,以应对不断增长的制程要求。

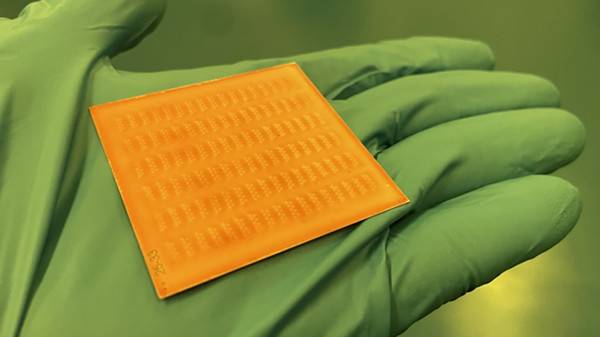

超声波喷涂技术用于半导体光刻胶涂层。与传统的旋涂和浸涂工艺相比,它具有均匀性高、微观结构良好的封装性和可控制的涂覆面积大小等优点。在过去的十年中,已经充分证明了采用超声喷涂技术的3D微结构表面光刻胶涂层,所制备的光刻胶涂层在微观结构包裹性和均匀性方面都明显高于传统的旋涂。

超声波喷涂系统可以精确控制流量,涂布速度和沉积量。低速喷涂成形将雾化喷涂定义为精确且可控制的模式,以在产生非常薄且均匀的涂层时避免过度喷涂。超声喷涂系统可以将厚度控制在亚微米到100微米以上,并且可以涂覆任何形状或尺寸。

关于驰飞

驰飞的解决方案是环保、高效和高度可靠的,可大幅减少过量喷涂,节省原材料,并提高均一性、转移效率、均匀性和减少排放。为企业提供围绕功能涂层的全套解决方案及长期技术支持,保证客户涂层稳定量产;针对特殊器械涂层需求,提供涂层定制研发服务;提供各类涂层代工服务。

杭州驰飞是超声镀膜系统开发商和制造商,产品主要应用于燃料电池质子交换膜喷涂、薄膜太阳能电池、钙钛矿、微电子、半导体、 纳米新材料、玻璃镀膜、 生物医疗、纺织品等领域。

英文网站:CHEERSONIC ULTRASONIC COATING SOLUTION

驰飞提供专业涂层解决方案:https://www.cheersonic-liquid.cn/